Nano Letters

刊发MODS团队单片集成的TexSe1-x短波红外光电探测器阵列的研究

2024年9月26号,Nano Letters在线刊发了华中科技大学唐江教授领衔的单片集成光电子器件与系统团队(MODS)题为《TexSe1–x Shortwave Infrared Photodiode Arrays with Monolithic Integration》的研究论文。论文第一作者为彭孟博士后、贺禹铭硕士生和胡宇煊硕士生,通讯作者为陈超副教授和唐江教授。论文第一单位为华中科技大学。

短波红外(SWIR, 1~2.5 μm)成像在生物成像、自动驾驶和安全监控等领域至关重要。传统半导体SWIR光电探测器主要由Ge、InGaAs和HgCdTe构成,这些材料需要在高温下采用复杂且昂贵的分子束外延或Bridgman方法进行沉积,限制了它们与硅读出集成电路(ROIC)的直接集成,导致成本增加和分辨率降低。尽管低温溶液处理的红外量子点、有机半导体以及GexSn1-x薄膜有望成为替代方案,但受到这些探测器检测性能和稳定性不足,它们的实际应用受到较大限制。因此,迫切需要开发可通过CMOS兼容工艺生长的SWIR材料。

碲-硒合金(TexSe1–x)因其简单的元素组成、可调带隙(0.35至1.9 eV)和低毒性而成为有前景的红外材料。其低熔点(220至450 °C)和低结晶温度(<165 °C)使其具备与ROIC一体化集成的潜力。然而,当前TexSe1–x薄膜光电探测器面临较大的暗电流问题,这对大规模阵列应用构成挑战。前期研究表明,ROIC工艺兼容的ZnO/TexSe1–x光电二极管的界面结构中,过量反应会导致元素扩散,从而引入额外的界面无序缺陷。此外,对于(hkl)取向(l≠0)的TexSe1–x薄膜,原子链的终端位于薄膜表面,导致在界面产生悬挂键缺陷。这些界面缺陷是影响暗电流的重要因素。因此,消除元素扩散并通过引入适当的界面层来钝化ZnO/TexSe1–x界面缺陷,以改善器件性能并降低暗电流,显得尤为重要和迫切。

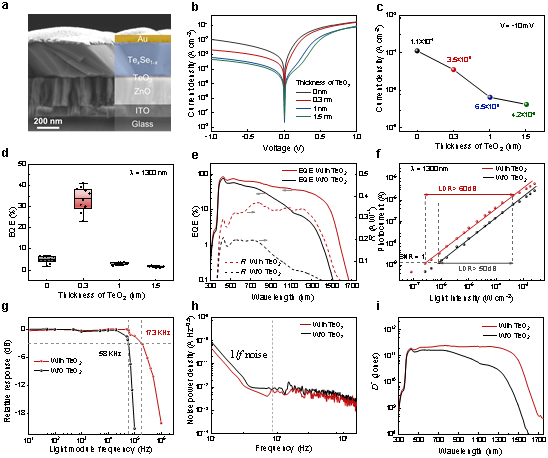

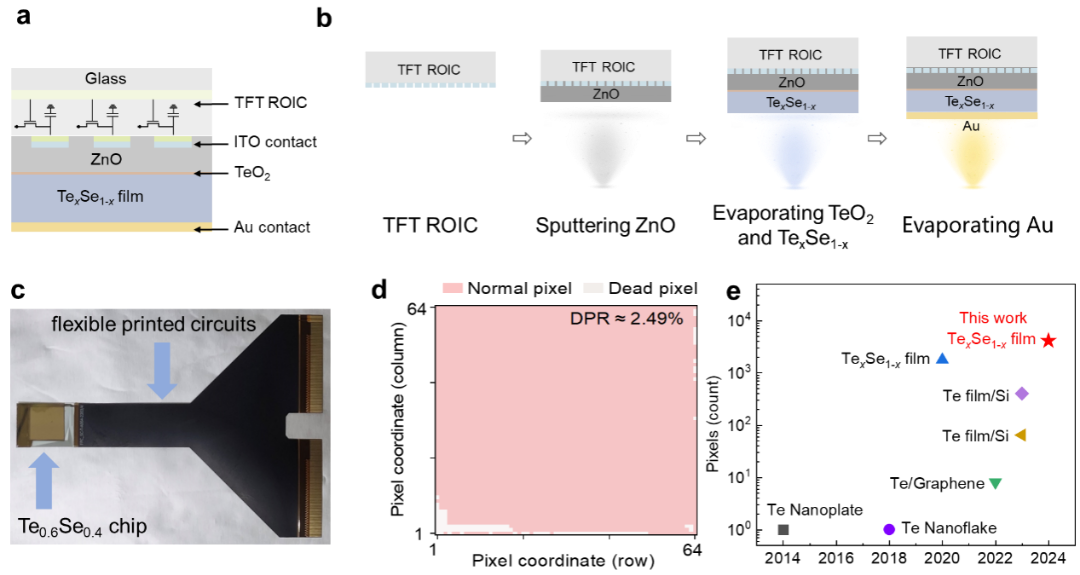

研究团队在ZnO/TexSe1–x界面引入了一层厚度为0.3 nm的非晶态TeO2层,成功阻止了元素扩散并钝化了界面悬挂键缺陷。通过二次离子质谱(SIMS)元素分布分析,确认了TeO2作为阻挡层有效阻碍元素扩散的能力。同时,TeO2作为钝化层的功能也得到了验证,表现为界面缺陷密度的降低和暗电流密度的显著抑制。经过TeO2修饰的ZnO/Te0.6Se0.4器件在性能上有了显著提升,宽光谱响应范围从原来的300~1500 nm拓宽至300~1700 nm,在1300 nm波长下,响应度从0.043 A W⁻¹提升至0.3 A W⁻¹,比探测率从2.86×10¹⁰ Jones提升至高达2.03×10¹¹ Jones。基于这些优异的结果,团队成功将TexSe1–x光电二极管单片集成到64 × 64非晶硅薄膜晶体管(TFT)读出集成电路上,并实现了短波红外成像应用,这是迄今为止基于TexSe1–x光电探测器的最大规模阵列。该研究为未来TexSe1–x红外成像器件在更高分辨率CMOS ROIC上的实现奠定了基础。

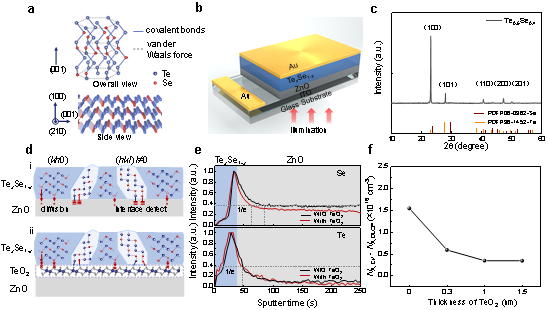

图1. ZnO/TexSe1-x光电二极管的界面问题。(a) TexSe1-x晶体结构的示意图。(b) Te0.6Se0.4光电二极管的器件结构。(c) 300 nm厚的Te0.6Se0.4薄膜的X射线衍射图。(d) ZnO/TexSe1-x光电二极管的界面示意图:(i) 未修饰的和(ii) 经过TeO2修饰的界面层。(e) 在有无TeO2修饰层情况下,ZnO/Te0.6Se0.4异质结中的Se和Te元素分布对比。(f) ZnO/Te0.6Se0.4界面处界面缺陷密度与TeO2厚度的关系。

图2. TeO2修饰层对ZnO/Te0.6Se0.4光电二极管探测性能的影响。(a) 器件的截面SEM图像,比例尺为200 nm。(b) 不同TeO2厚度下ZnO/Te0.6Se0.4器件的J-V 曲线。(c) 不同TeO2厚度下ZnO/Te0.6Se0.4器件的暗电流密度。(d) 在1300 nm波长下,不同TeO2厚度器件的外量子效率(EQE)。(e) 器件的EQE和光响应度随光波长变化的曲线。(f) 在1300 nm波长下的线性动态范围(LDR)。(g) 在-10 mV偏压下的-3 dB响应带宽。(h) 在-10 mV偏压下的噪声电流与频率的关系。(i) 比探测率(D*)随波长变化的曲线。

图3. Te0.6Se0.4成像芯片的设计与单片集成的制备。(a) Te0.6Se0.4成像芯片的示意图。(b) 单片集成工艺的示意图。(c) 单片集成的Te0.6Se0.4成像芯片的照片。(d) 在64 × 64 TFT阵列中4096个像素的信号分布,死像素率(DPR)约为2.49%。(e) 基于TexSe1-x的光电探测器阵列中像素计数的统计数据。

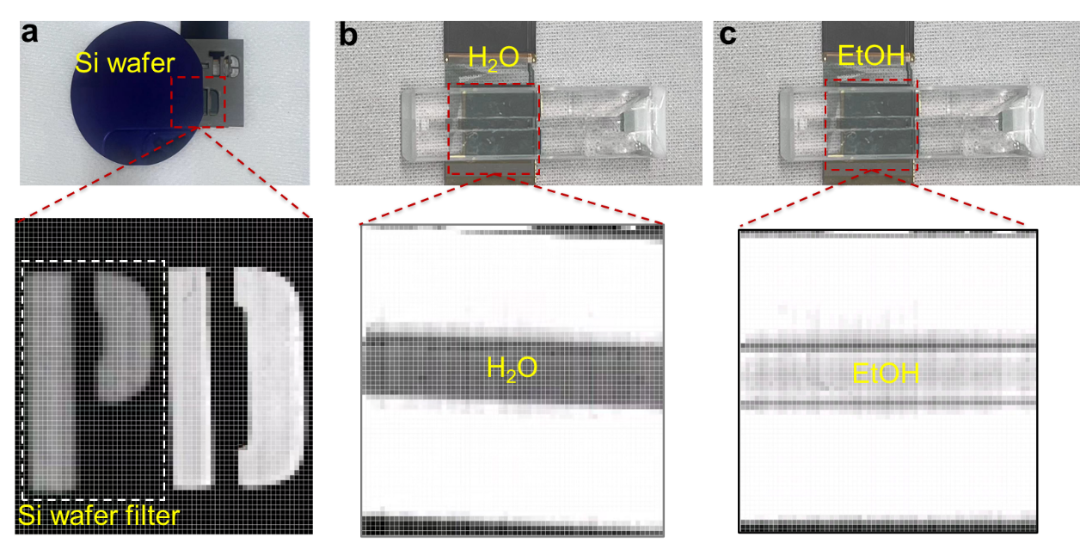

图 4. 利用Te0.6Se0.4 成像芯片进行红外成像。(a) 通过硅片滤光对金属“PD”图案的红外成像。(b, c) 对水(b)和乙醇(c)的可见光和红外成像。

该工作得到国家自然科学基金、中央高校基本科研业务专项资金、国家重点研发计划项目、中国博士后科学基金项目等项目资助。感谢华中科技大学微纳制造与表征中心在器件制造和表征方面的支持,感谢华中科技大学分析测试中心在材料及器件表征方面的支持。

https://pubs.acs.org/doi/abs/10.1021/acs.nanolett.4c03728